SOC

SOC架构是做嵌入式BSP、Kernel开发、以及Stability分析人员需要了解的一个知识点,不需要太深入,但是一些基本点还是需要知道的。

从两个简单例子看SOC架构

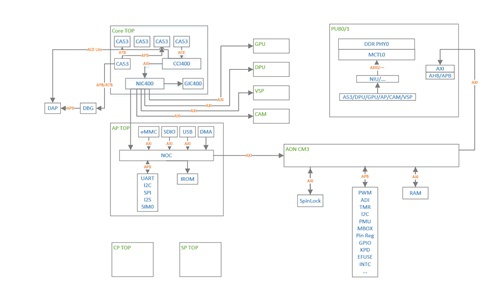

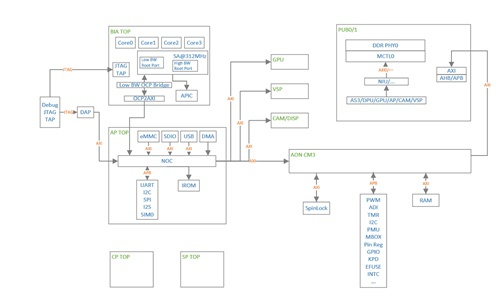

SOC架构示意图

以下两幅图是ARM和X86架构的SOC示意图,注意,这只是示意而已很多地方是错误的。

一般在ARM平台的SOC上会包含如下表所示的网元逻辑:

| 功能模块 | Description | Usage |

|---|---|---|

| Core | 如CA7、A53、CA57、CM4、CR5等等 | CPU核心 |

| BUS | I2C、apb、ahb、axi、spi、gpio等等 | 系统总线 |

| Metrix | NIC、NOC、AON、CCI | 矩阵和逻辑网元 |

| Bridge | apb2axi、async_bridge、 | 逻辑桥电路 |

| SOC Controller | intc、DMA、irom、iram、uart、spinlock、mailbox | 各种控制器IP |

| Register | global register | SOC系统级全局寄存器 |

| Clock && Reset | clock(UPLL=》USB、MPLL=》FCLK、HCLK、PCLK) && reset(watchdog) | 时钟和复位控制 |

| Debugger | busmonitor、jtag、coresight | 调试电路 |

| Device Controller | USB、DDR、DPU、PMU、GPU、GSP、VSP、DPU(DSI)、eMMC、UFS、ISP、SDIO、CAM | 主要是接mother board上外设的 |

SOC相关常见总线

SOC片内总线

这里片内总线主要是指SOC内部链接各个逻辑网元的系统总线,按照ARM架构定义,大概有如下几种:

片外总线

参考文档

@2018-03-07 18:50

Comments